# Breaking Barriers: Expanding GPU Memory with Sub-Two Digit Nanosecond Latency CXL Controller

Donghyun Gouk, **Seungkwan Kang\***, Hanyeoreum Bae, Eojin Ryu, Sangwon Lee, Dongpyung Kim, Junhyeok Jang, Myoungsoo Jung

#### High -Level Summary

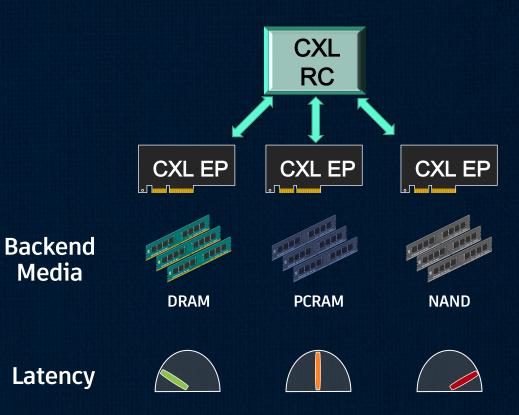

We introduce the potential of GPU storage expansion utilizing CXL

- Diverse backend media

- Load/store access

to EPs

We designed and prototyped a CXL-integrated GPU

- Memory map

- Initialization

- CXL root complex

- GPU architecture

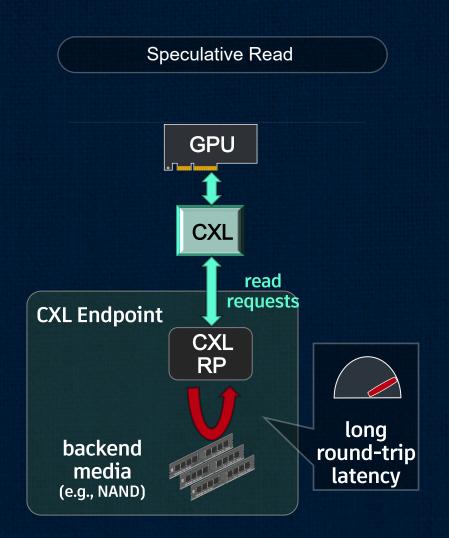

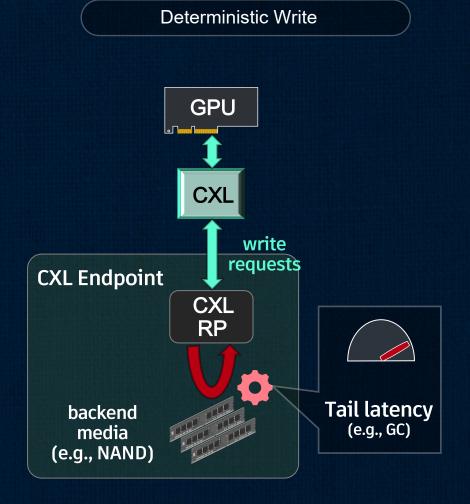

We further minimized the impact of backend media latency

Speculative read

- Minimize read

latency

Determinstic store

- Mitigate tail

latency of writes

#### 1. GPU Memory Expansion and Potential of CXL

2. Designing a CXL-integrated GPU

3. Mitigating Backend Media Latency

4. Evaluation Results

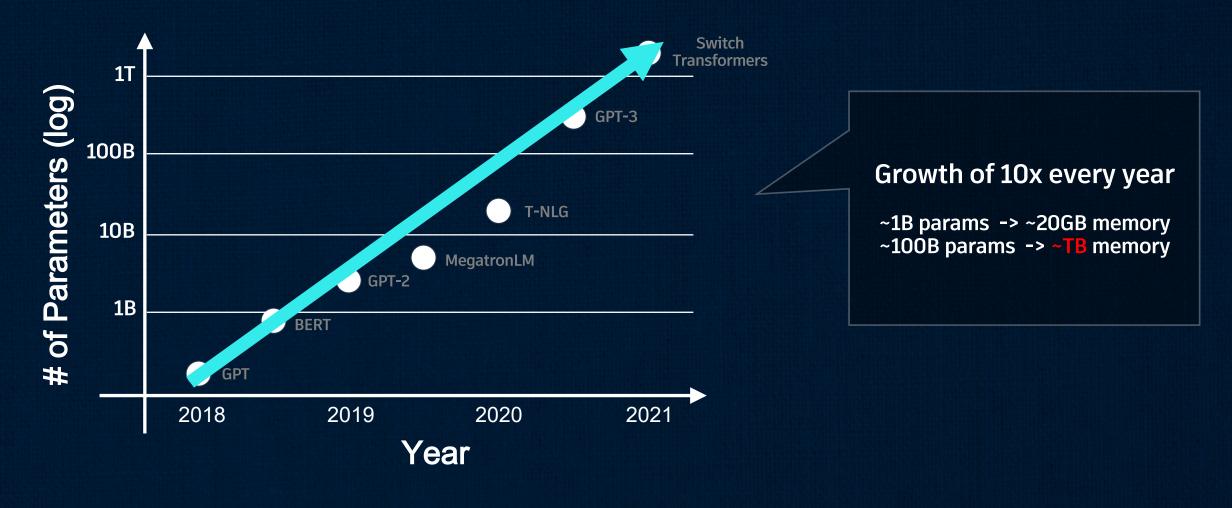

#### **Growth of GPU Memory Requirements**

#### **GPU Memory Expansion**

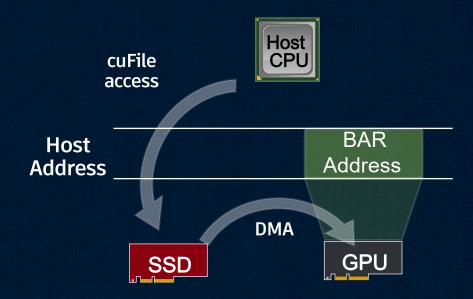

#### **Storage Solutions**

(e.g., GPU-Direct Storage)

- Enables large-scale models via storage

- ✓ Direct access to storage

- x Complexity of usage (Manual handling)

- x Disparity in I/O granularity

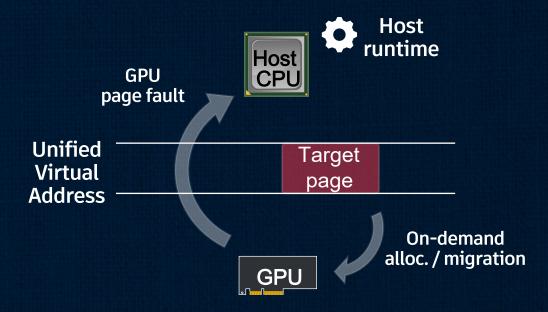

#### **Host Memory Solutions**

(e.g., Unified Virtual Memory)

- ✓ On-demand allocation/migration

- ✓ Wide adoption (e.g., Tensorflow, DGL)

- **x** Requires host runtime

- **X** Induce performance bottlenecks

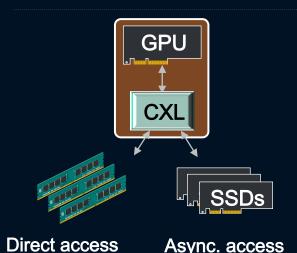

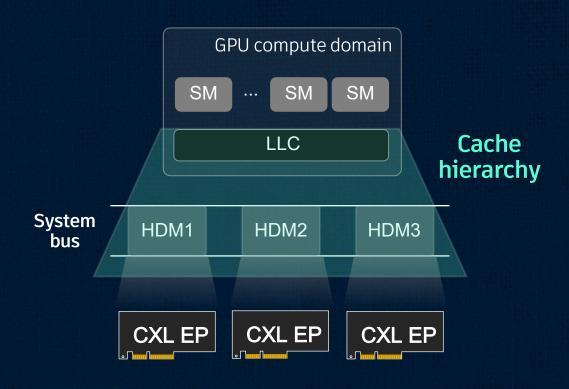

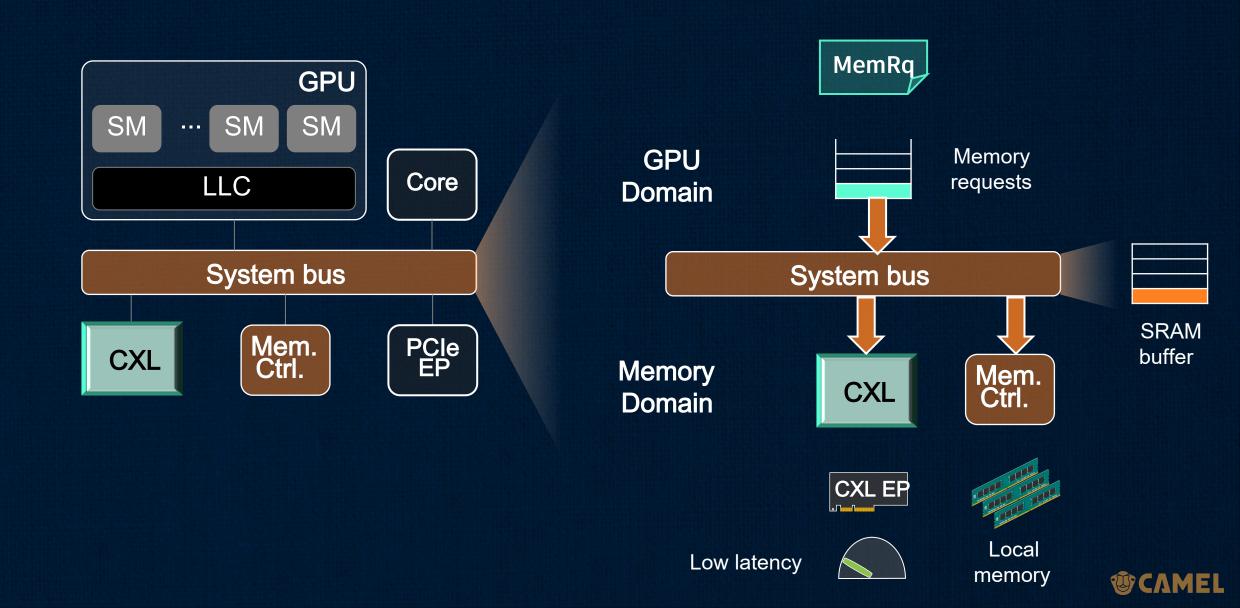

### Potential of CXL -integrated GPUs

Direct access to EPs via ld/st memory access

Asynchronous communication w/ media

1. GPU Memory Expansion and Potential of CXL

2. Designing a CXL-integrated GPU

3. Mitigating Backend Media Latency

4. Evaluation Results

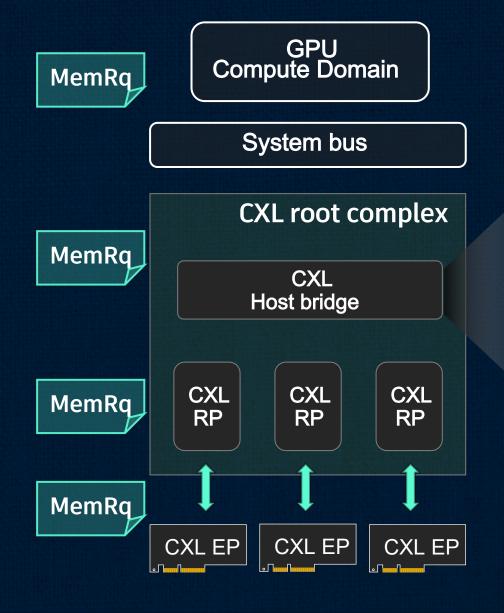

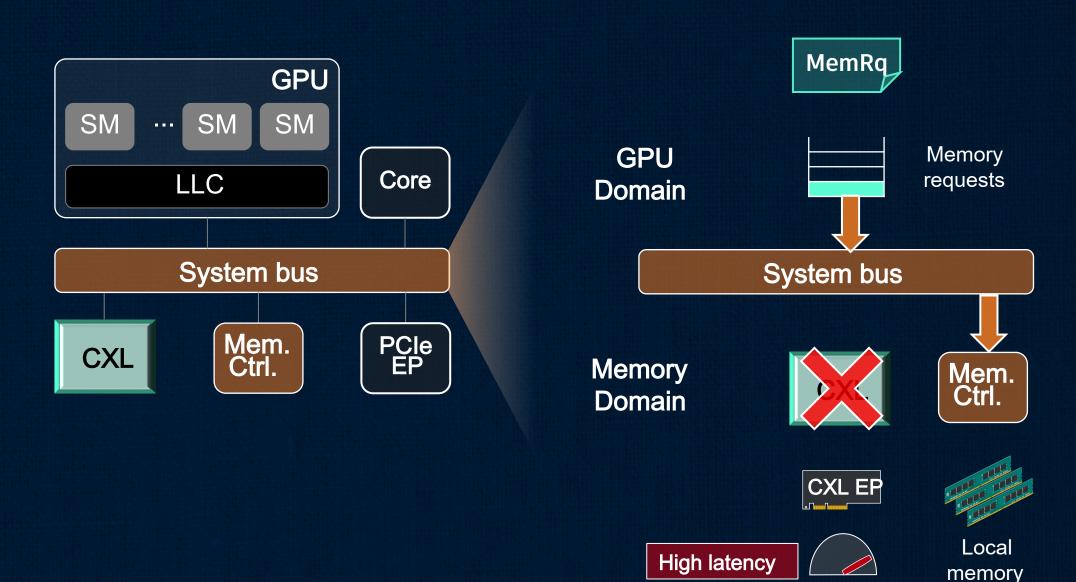

#### Challenges

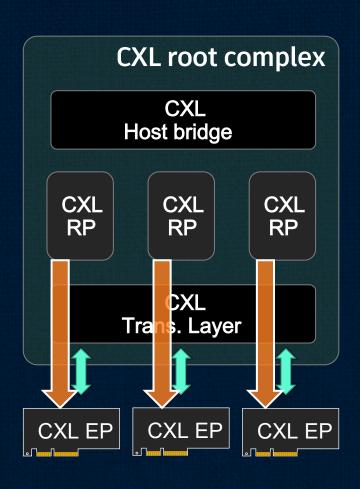

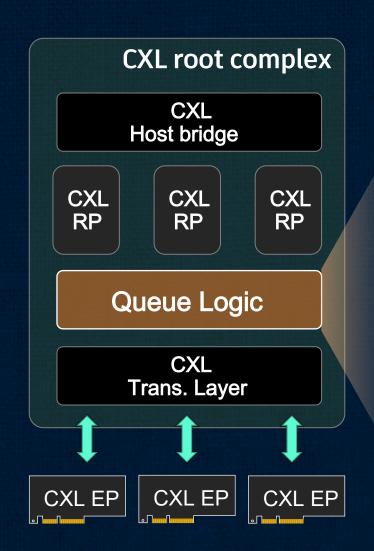

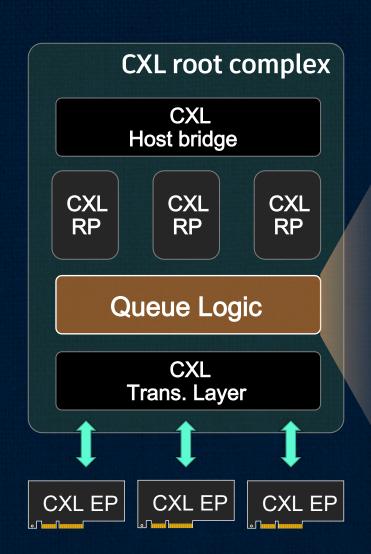

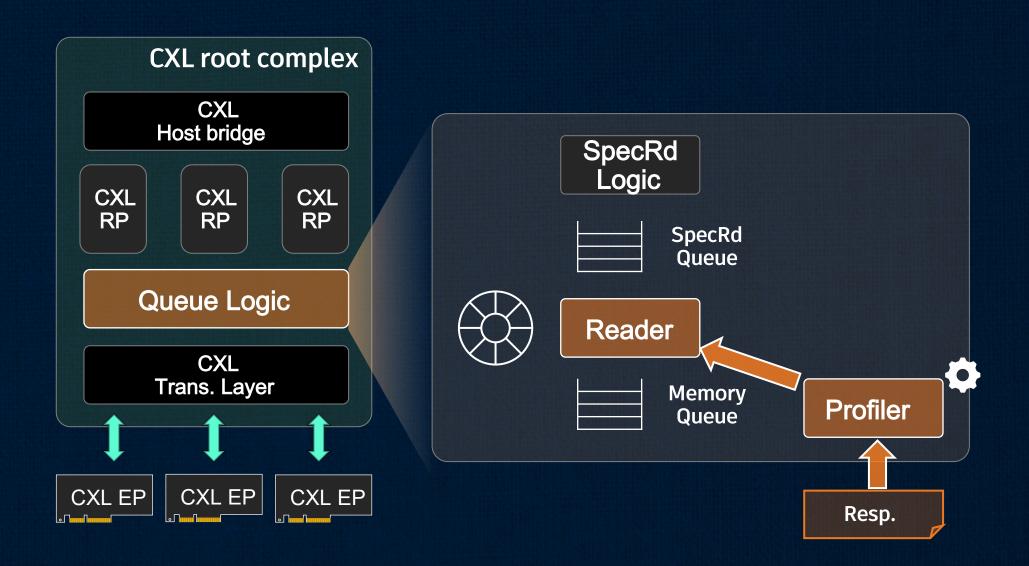

#### **CXL** root complex

How should we design a CXL controller for memory expansion?

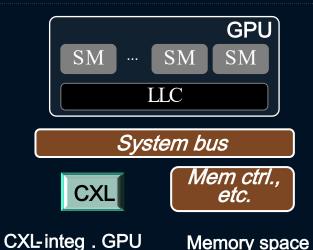

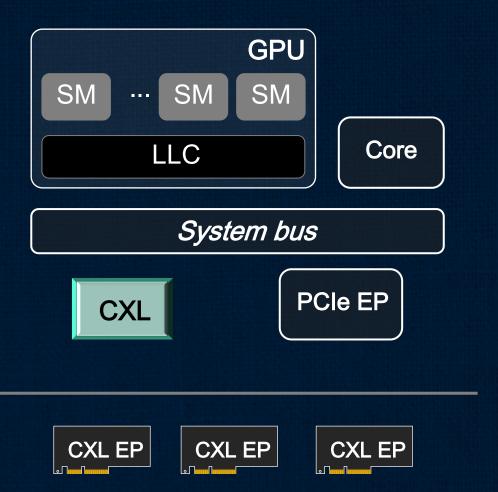

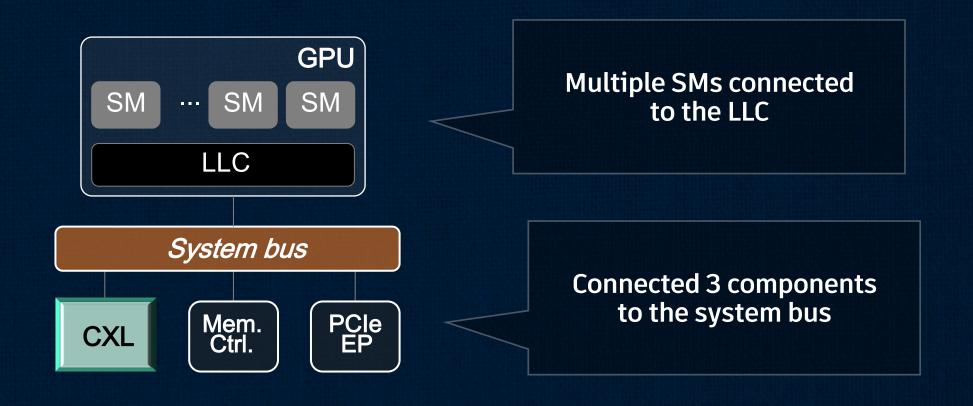

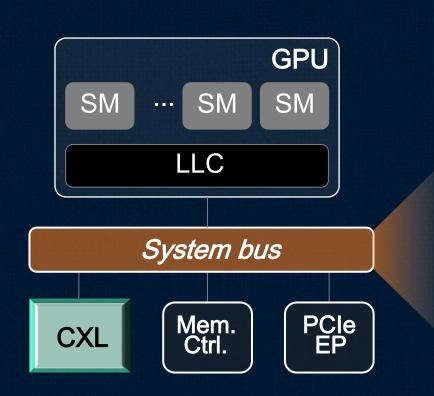

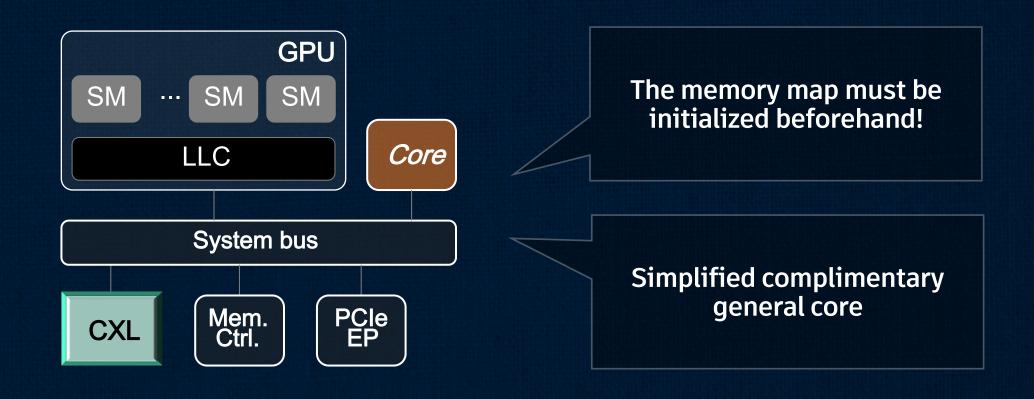

# **CXL-integrated GPU architecture**

How should we connect the CXL controller to the GPU?

System initialization

System bus memory map for routing

Diverse memory backends

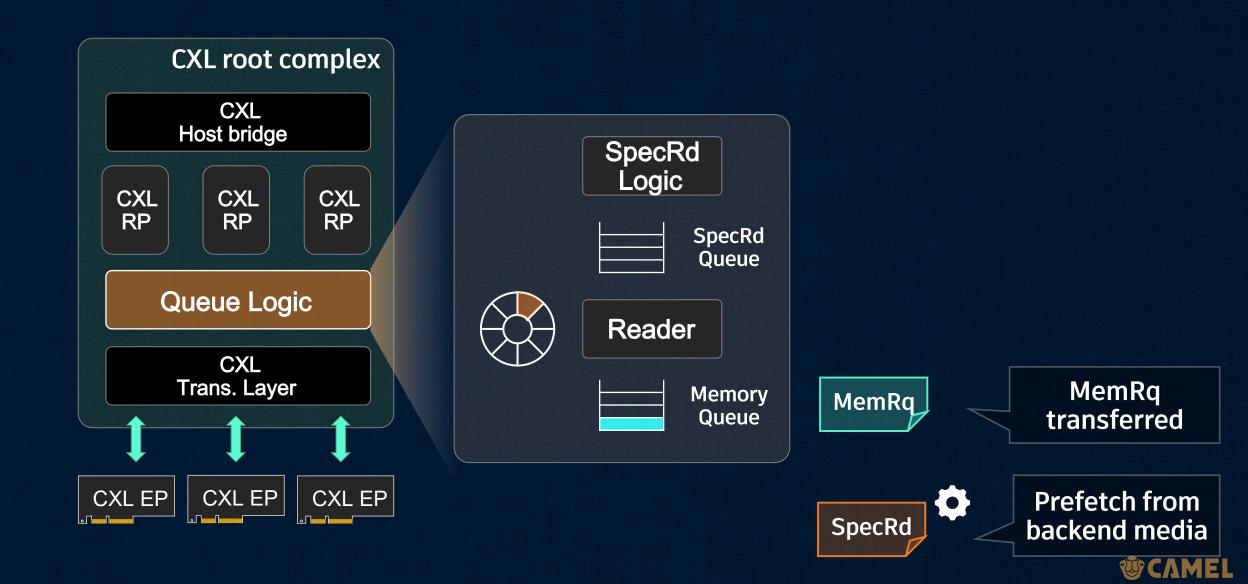

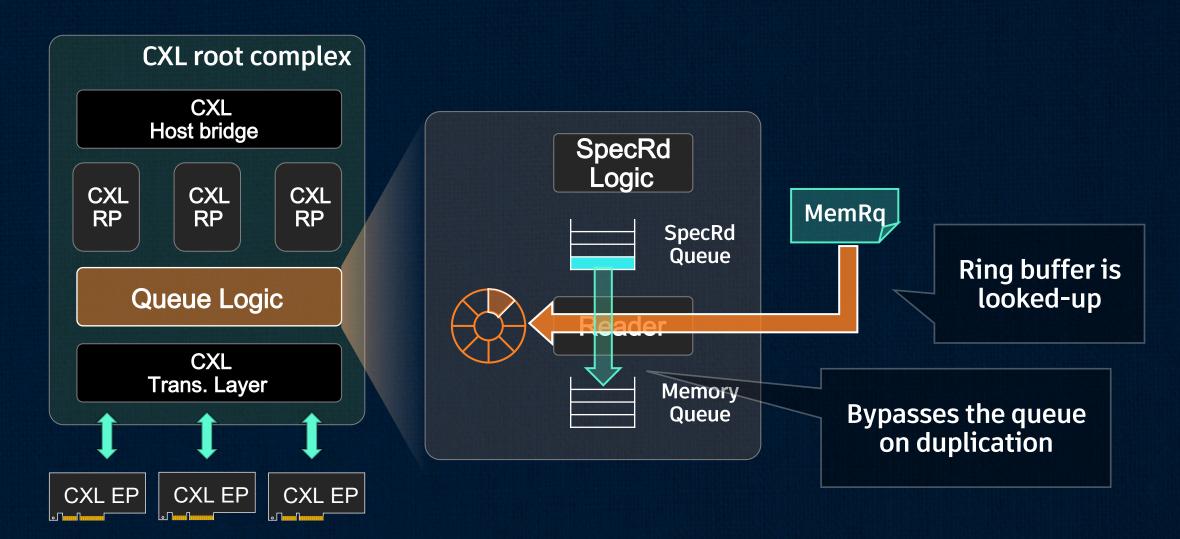

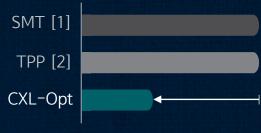

#### CXL Root Complex - E2E Data Movement

Initiates a memory request

**HDM Decoder**

| HPA         | RP# |

|-------------|-----|

| 0x00 -0x0A  | 0   |

| 0x10-0x3A   | 1   |

| 0x50 - 0x6A | 2   |

Lookup HDM decoder

Forwarded and interpreted

Carried by the FlexBus

#### **CXL-integrated GPU Architecture**

#### **CXL-integrated GPU Architecture**

GPU Control

Local Memory

Host Memory

CXL CHBCR\*

HDM

5 segments of system bus

#### System Initialization

1. GPU Memory Expansion and Potential of CXL

2. Designing a CXL-integrated GPU

3. Mitigating Backend Media Latency

4. Evaluation Results

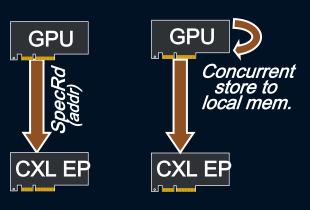

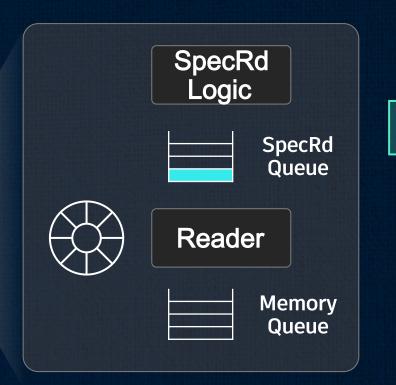

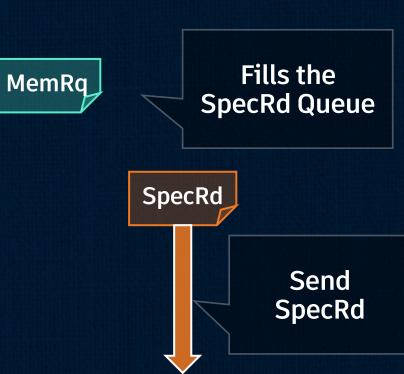

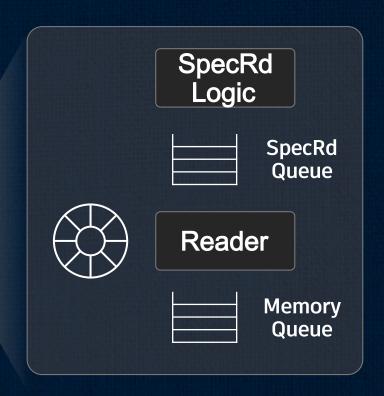

# Mitigating Backend Media Latency

Provide hints about in-coming memory requests

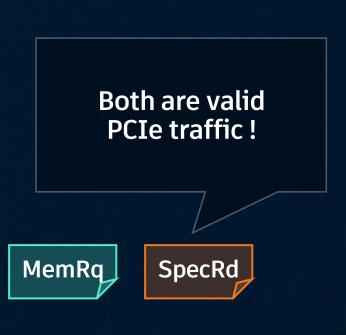

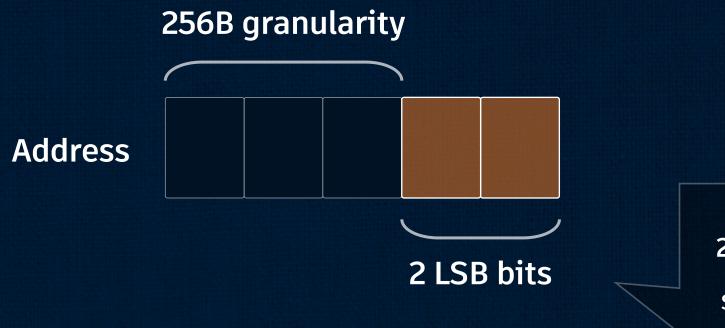

### Speculative Read - Optimizations

256B ~ 1024B SpecRd

Support GPU's large reads

### Speculative Read - Optimizations

#### Deterministic Store - Idle Scenario

# Deterministic Store - Tail Latency Scenario

# Deterministic Store - Tail Latency Scenario

1. GPU Memory Expansion and Potential of CXL

2. Designing a CXL-integrated GPU

3. Mitigating Backend Media Latency

4. Evaluation Results

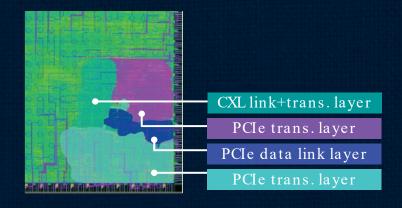

### **Evaluation Methodology**

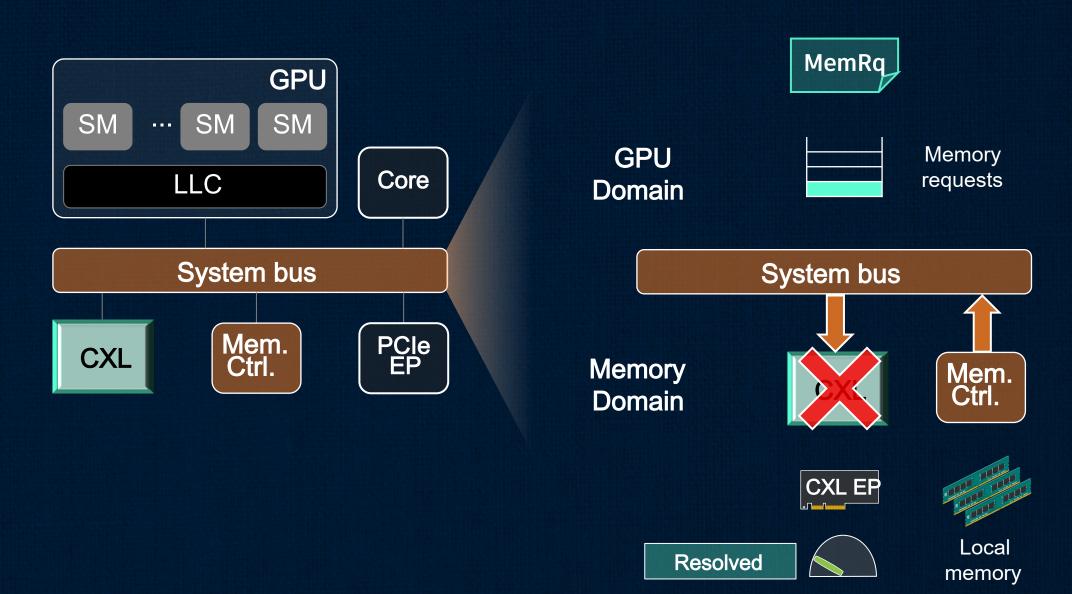

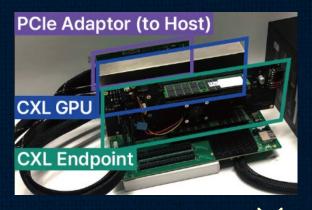

#### ASIC Prototype (CXL Controller)

<Round-trip latency>

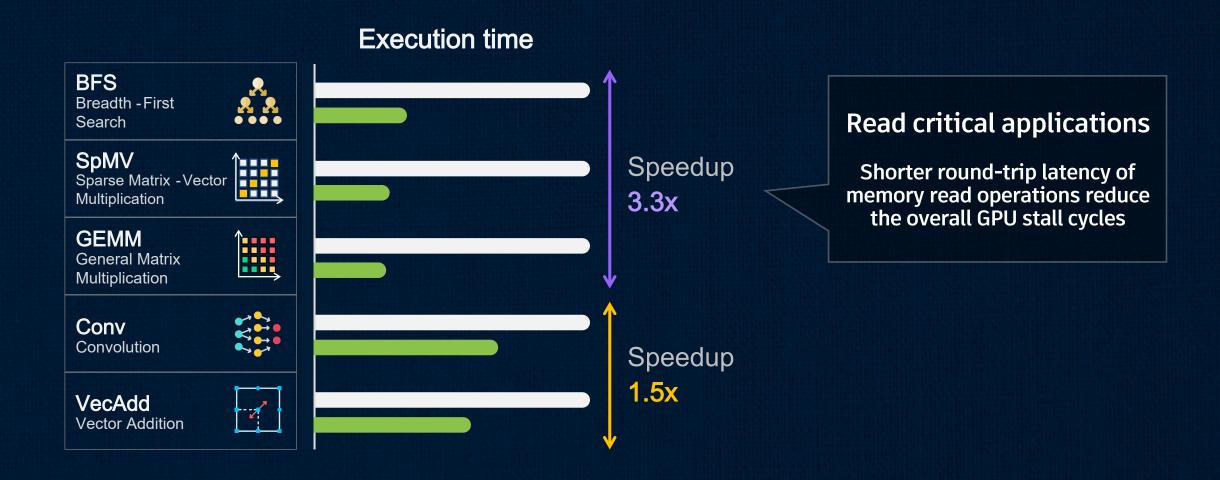

The proposed CXL controller showed >3x shorter latency

- GPU: SMs x 2, cores x 4

- PCle 5.0 x 8

- CXL 3.1

| Compared systems |                                             |

|------------------|---------------------------------------------|

| UVM              | Page fault -based virtual memory management |

| CXL-GPU          | CXL with sub-two digit nanosecond latency   |

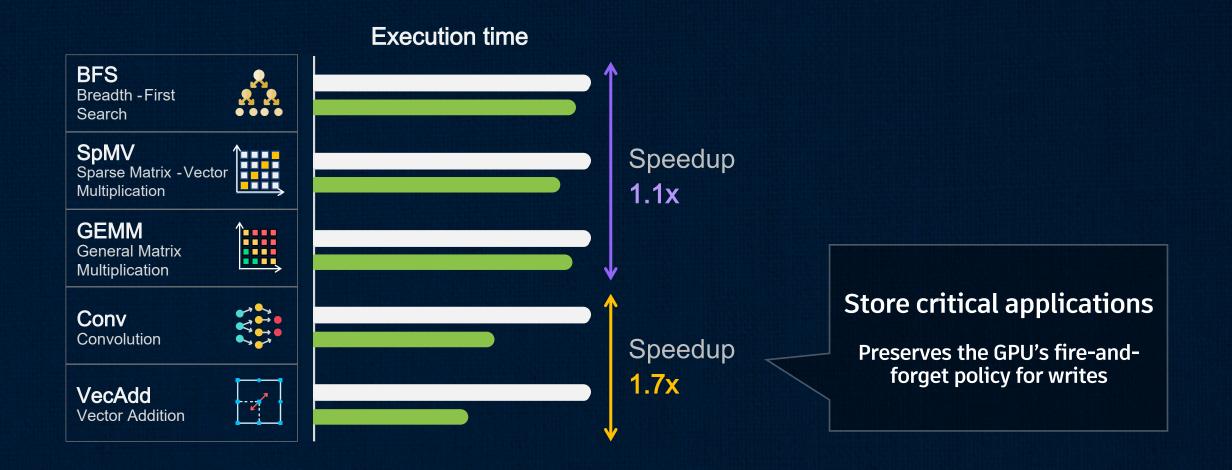

#### Overall Performance

#### **Deterministic Store**